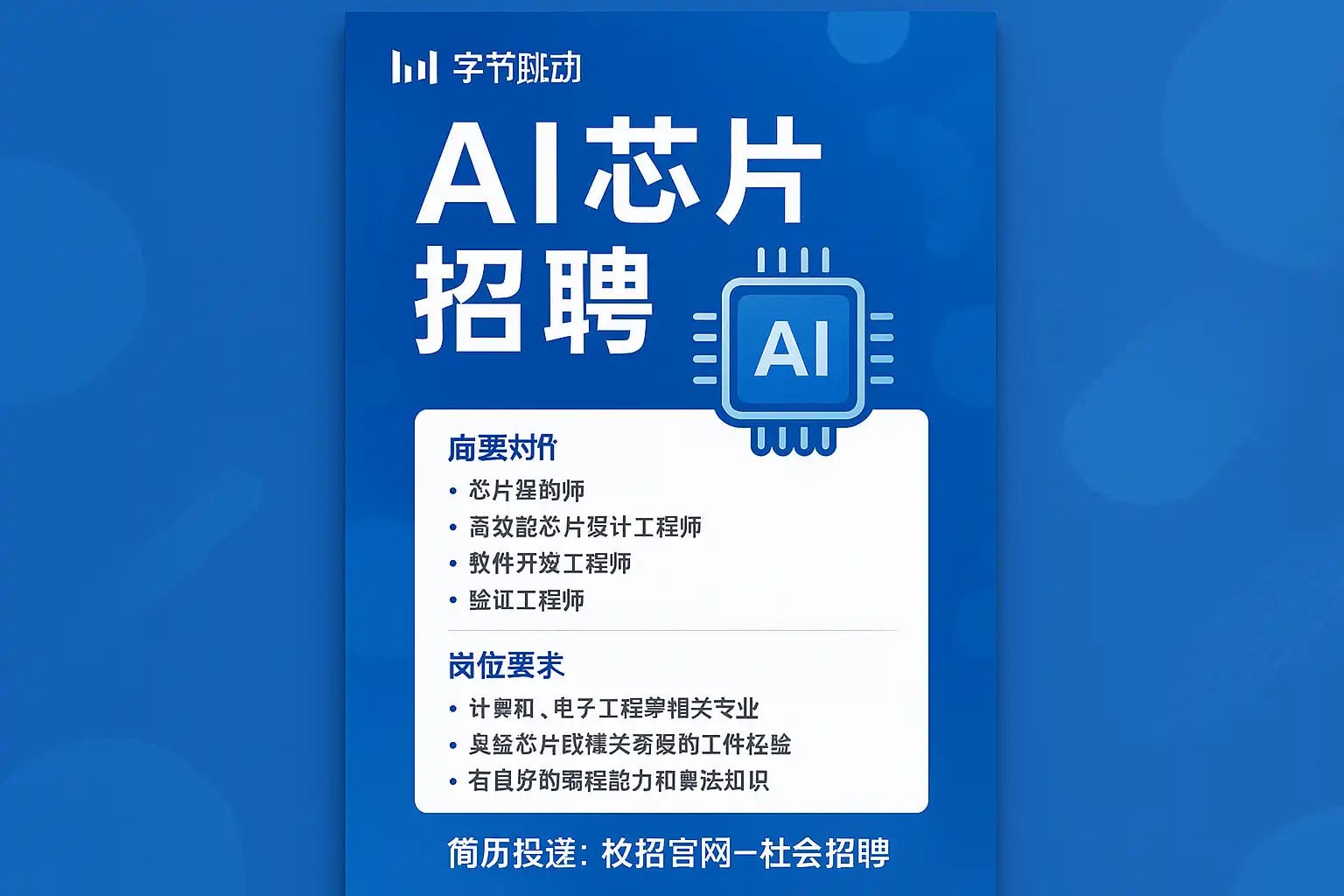

字节跳动AI芯片招聘最新信息,如何抓住就业机会?

摘要:字节跳动AI芯片招聘的核心机会集中在“加速器架构/编译器/驱动/算子/验证/后端实现”等岗位,竞争侧重工程落地与性能指标。抓住机会的关键是:1、对齐岗位能力模型、2、跑对渠道与节奏、3、用硬核作品集证明匹配度。请用项目化成果展示算力、延迟、吞吐、能效等可量化闭环,用关键词精准检索并争取内推,搭配系统化面试准备与投递跟踪,提升命中率与转化率。

《字节跳动AI芯片招聘最新信息,如何抓住就业机会?》

一、岗位地图与能力模型

AI芯片团队岗位通常覆盖“从架构到落地”的全栈闭环:体系结构定义、RTL前端、验证、后端、DFT、CAD/EDA、驱动/固件、编译器/算子、性能与调优、平台化部署。以下表格梳理岗位—核心技能—可提交证据,便于快速对标与准备。

| 岗位方向 | 核心技能栈 | 作品集/证据(可量化) |

|---|---|---|

| AI加速器架构(训练/推理) | 指令/算子集设计、数据流/NoC/缓存/带宽建模、HBM/DDR/片上存储、并行与流水、功耗/面积/性能(PPA)权衡、工作负载特征(GEMM/Attention/Conv) | 算法到硬件映射白皮书、性能模型(含Roofline/带宽敏感性)、Topo/算子融合设计、PPA对比曲线、仿真报告 |

| 数字前端RTL | Verilog/SystemVerilog、时序/握手机制、低功耗设计、Lint/CDC、模块化与可综合优化 | 关键模块RTL(MAC阵列/NoC/缓存控制器)与testbench、综合后时序报告、代码覆盖率 |

| 验证(DV) | UVM、约束随机、功能覆盖率、断言SVA、仿真/回归、Bug归因 | 覆盖率矩阵、Bug闭环报告、测试向量设计、CI回归构建 |

| 后端实现(PD/PI) | Floorplan/Placement/CTS/Route、时序收敛、IR/EM/热分析、低功耗、工艺/库理解 | 收敛前后对比(WNS/TNS/功耗/面积)、拥塞热力图、脚本与方法学 |

| DFT/可测性 | Scan/MBIST/JTAG、可测性约束、产测良率分析 | DFT插入报告、覆盖率与良率数据、量产复盘 |

| CAD/EDA | 流程编排、工具二次开发(Tcl/Python/C++)、PDK适配、可复用方法学 | 自动化脚本套件、效率提升指标、跨项目可复用度 |

| 编译器/图优化 | MLIR/TVM/XLA、算子划分/融合/调度、Quantization/Pruning、AutoTVM/Ansor | 端到端模型在特定后端的加速比、吞吐/延迟/能效提升、算子库Benchmark |

| 内核/算子/库 | CUDA/ROCm/自研后端Kernel、GEMM/Conv/Attention内核调优、张量布局、向量化 | Kernel性能对标(FP16/INT8)、Roofline占位、Cache命中率/带宽利用 |

| 驱动/固件 | Linux内核/PCIe/NUMA/IOMMU、中断/内存管理、调度与多租户 | 驱动性能与稳定性指标、资源调度策略、大规模压力与可靠性报告 |

| 性能工程/系统化 | Profiling/Tracing、瓶颈定位、QoS/功耗管理、A/B实验 | 性能剖析报告、优化前后关键KPI(TOPS/W、TP99、吞吐) |

| 平台/分布式 | 集群调度(K8s/Slurm)、编排、弹性与容错、资源利用率 | 资源利用率提升、成本/功耗节约、调度策略验证 |

要点:字节跳动务实工程导向强,除“能做什么”外,尤其看重“做到多快、多稳、多省(时延/吞吐/故障率/能效/成本)”。

二、能力对标清单(硬技能+软技能)

- 通用硬技能

- 算力与带宽:Roofline、算子算强/算弱、存算比、带宽/延迟敏感性分析

- PPA三角:面积/功耗/性能的约束权衡与实验方法

- 工具链:常用EDA(Synopsys/Cadence/Mentor)、CI/CD、Profilers(nsys、nvprof、perf)

- 代码质量:模块化、可测性、覆盖率、静态检查与规范

- 岗位专项要点

- 架构:工作负载画像→数据流→存储/NoC→指令/算子→性能模型→硬件/软件协同

- RTL/DV:时序/握手/背压、协议一致性、随机/定向用例设计、断言策略

- 后端:时钟/复位/电源域、时序与串扰、物理可实现性与方法学沉淀

- 编译器/算子:IR/Pass、算子融合、张量布局、量化标定、AutoTuning

- 驱动/固件:DMA/中断/内存池、并发与死锁、NUMA亲和、性能调度

- 软技能

- 问题分解/闭环:明确KPI、最小可行实验、迭代节奏、风险预案

- 跨团队协同:架构-编译器-内核-后端-平台的接口契约与交付边界

- 文档与评审:PRD/Design Doc/Benchmark协议、复盘可追溯性

快速自检(勾选≥80%优先投递):

- 是否有≥2个端到端可复现实验,能证明“指标提升+可重复”?

- 是否能用数据解释每次优化的瓶颈迁移路径?

- 是否能回答“为什么不是另一个方案”及其代价曲线?

三、招聘渠道、节奏与关键词检索

有效渠道与节奏决定“被看见”的概率。建议多通道并行、投递分批AB测试。

| 渠道 | 触达速度 | 命中率 | 适用场景 | 关键动作 |

|---|---|---|---|---|

| 官方招聘(字节跳动招聘官网) | 高 | 中-高 | JD最全、流程标准 | 关键词检索、定向投递、订阅提醒 |

| 内推(校友/同事/社区) | 中 | 高 | 简历竞争激烈时 | 定制化匹配、补充项目解读 |

| 猎头/机构 | 中 | 中 | 级别较高/跨城机会 | 明确级别与方向、保护隐私 |

| 开源/学术(GitHub/ArXiv/顶会) | 中 | 中-高 | 编译器/内核/工具链 | 用PR/Issue/Repo让简历被动“显眼” |

| 校招/实习专场 | 高峰期 | 高 | 在校/应届 | 提前打磨作品集和技术博客 |

关键词建议(中英文组合提升召回):

- 芯片/加速器:AI加速器、推理/训练、NoC、HBM、数据流、编译器后端、算子优化

- 栈向:RTL、UVM、DFT、PD/PI、Timing Closure、Placement、CTS、IR/EM

- 软硬协同:MLIR、TVM、XLA、Kernel、GEMM、Attention、INT8/FP16/BF16、Quantization

- 平台侧:Driver、PCIe、IOMMU、NUMA、Scheduler、Profiling、K8s/Slurm

投递跟踪与ATS优化

- 简历布局:前20%展示可量化成果(x%延迟下降、y%吞吐上升、z%能效提升)

- 关键词匹配:与JD关键术语对齐,避免堆砌,保持证据链

- 进度追踪:使用表格记录“岗位-日期-反馈-下一步-跟进人”,每7天跟进一次

- 多数企业使用ATS系统管理投递。部分公司或合作方采用i人事(支持候选人账号登录查询状态): https://account.ihr360.com/ac/view/login/#/login/?source=aiworkseo;

四、作品集与项目证明材料(硬核取胜)

准备原则:端到端、可复现、可量化、可审计。避免敏感数据,必要时用公开模型/数据集替代。

作品集内容结构(建议5-12页PPT+代码仓)

- 问题定义与业务KPI:例如“B端推理延迟TP99≤10ms,吞吐≥X QPS,功耗≤Y W”

- 架构/方案:数据流/存储层次/算子融合/并行策略/调度

- 实验设计:对照实验、采样方法、统计置信区间

- 指标与曲线:Latency/QPS/TOPS/W/WNS/TNS/面积/功耗/覆盖率

- 代价与权衡:对比替代方案,说明资源与维护成本

- 事故与复盘:故障模式、回滚策略、灰度验证

- 工程化:CI/CD、自动化脚本、文档可重复

示例表达模板

- 将GEMM内核从FP32→INT8量化并配套重训练,在A模型上吞吐+2.3x,TP99从24.7ms降至10.8ms,精度ΔTop1≤0.3%,GPU/自研后端双轨对齐

- 为MAC阵列设计片上缓存复用与预取策略,带宽占用-38%,阵列利用率+21%,同等面积下功耗-12%

- 开发UVM环境与约束随机用例,功能覆盖率从82%→96%,关键Bug逃逸率归零,回归时间-35%

五、面试流程与题型覆盖(如何准备)

常见流程:简历筛选→技术电话→专项深挖(2-3轮)→交叉面→综合/HR。准备重点见下表:

| 面试环节 | 题型范围 | 准备要点 |

|---|---|---|

| 技术电话 | 简历项目、KPI、工具链 | 3-5个可讲透的项目,指标与实验细节背得下 |

| 架构/系统 | 数据流/存储层次/NoC/并行/性能模型 | 用白板推导,画出带宽与算力瓶颈路径 |

| 代码/RTL/Kernel | Verilog/C++/CUDA/并发与内存 | 现场小题/走查,强调可测性与鲁棒性 |

| 验证/方法学 | UVM/覆盖率/断言/回归 | 覆盖率闭环、Bug案例、CI实践 |

| 后端/时序 | PnR/时序收敛/IR/EM | 出示收敛数据、脚本与权衡思路 |

| 编译器/优化 | IR/Pass/算子融合/量化 | 选一个算子做数据化讲解,附代码片段 |

| 交叉面 | 跨域沟通与边界定义 | 用接口契约描述跨团队协作场景 |

| HR/综合 | 动机/抗压/成长性/风险 | STAR法+复盘样例,透明表达预期 |

高频问题库线索

- 画出Transformer推理的数据流,标出存储/带宽瓶颈与优化入口

- 解释Roofline模型,给定峰值算力和带宽推导实际可达性能

- 讲一个覆盖率从不足到达标的案例,如何设计约束随机与断言

- 给定一个Kernel的访存模式,如何改造以提升Cache命中与并行度

- 时序收敛失败的前三类原因?如何用脚本批量定位与修复

六、校招/实习与社招的差异化策略

- 校招/实习

- 时间线:提前批(7-8月)→秋招(9-10月)→补录(11-12月/次年春)

- 核心:竞赛/论文/开源/课程大作业工程化,1-2个可复现项目胜过泛泛课题

- 行动:导师/社群争取内推;把实习/课程项目改造为“简化可复现”公开仓

- 社招

- 核心:业务闭环与工程影响力,端到端交付与跨团队协作

- 行动:梳理“问题-方案-指标-代价-复盘”,准备保密可讲版本;并行多职位投递

12周准备里程碑(可前后滑动)

- 第1-2周:岗位画像与差距评估,确定2条主线(如编译器+内核/RTL+DV)

- 第3-6周:打磨作品集与复现实验,建立Benchmark流水线

- 第7-8周:模拟面试/代码走查/论文精读(TVM/MLIR/NoC/Attention系统化)

- 第9-12周:批量投递+内推,AB版简历与材料,节奏性跟进

七、跨岗转入与差距补齐路径

- CUDA/深度学习工程师 → 编译器/内核

- 重点:IR/Pass、算子融合、向量化与张量布局、AutoTuning

- 练习:用TVM/MLIR为GEMM/Attention做端到端优化,记录性能曲线与调度日志

- 后端/验证工程师 → AI芯片实现

- 重点:面向AI工作负载的时序与功耗收敛、NoC/缓存约束、UVM覆盖闭环

- 练习:搭建简化MAC阵列设计→从RTL到PnR的完整流水线

- AI平台/系统 → 驱动/性能工程

- 重点:PCIe/NUMA/内存管理、调度与隔离、Profiling与瓶颈定位

- 练习:构建可重复的压测环境,输出多维度KPI与优化报告

学习与工具清单

- 工具:Verilator/VCS、Vivado/Quartus、Synopsys/Cadence、nsys/perf、TVM/MLIR、K8s/Slurm

- 资料:硬件加速器论文(MLSys/ISCA/HPCA)、编译器栈论文与教程、开源内核仓(cutlass/flash-attention/oneDNN)

- 方法:每周一篇复现,附指标/脚本/失败记录

八、城市与组织协同、合规注意事项

- 办公与协同:大厂芯片团队常分布在一线城市研发集聚区(如北京/上海/深圳等),跨地协同强调接口契约与文档先行

- 合规与安全:开源许可证合规(Apache/BSD/GPL),数据安全与保密边界,硬件与EDA许可合规;对外分享材料需做脱敏与匿名化

- 供应链与测试:工艺/封装/测试外协沟通,量产良率与故障复盘流程意识

九、薪酬结构、级别判断与Offer决策(不空谈数值)

- 结构要点:Base+Bonus+股权/期权+补贴(餐/房/交通/通信)+签字金(如有)

- 评估维度

- 成长曲线:岗位复杂度/主责模块、技术栈稀缺度、导师与评审文化

- 影响力:面向核心KPI的路径是否清晰(延迟、吞吐、能效、稳定性)

- 资源与生态:工具链、数据/算力、跨团队资源获取难度

- 风险:角色稳定性、上下游依赖、路线确定性与切换成本

- 谈判清单:级别/title、试用与评估标准、到手节奏(税/社保/公积金)、远程与出差政策、保密与竞业

十、行动清单(4周快启版)

- 第1周

- 定义目标岗位两条主干(如“编译器/内核”或“RTL/验证”)

- 产出1页岗位对标表:技能—证据—补齐计划

- 整理简历Top区:3条可量化项目(指标+方法+对比)

- 第2周

- 复现1个公开算子或子系统(GEMM/Attention/NoC),输出基线指标

- 撰写技术博文1篇,记录方法与数据

- 建立投递追踪表与关键词库

- 第3周

- 小范围投递(5-8个岗位)+寻求2个内推

- 模拟面试2次(专项+交叉),优化答题结构

- 作品集补充“代价与权衡”章节

- 第4周

- 扩大投递面(10-15个岗位),AB测试简历版本

- 复盘面试反馈,针对薄弱环节做专项训练

- 准备HR面材料(动机、期望、风险应对)

总结:

- 机会在哪里:加速器架构、编译器/算子、内核/驱动、RTL/验证/后端、性能与平台工程,工程落地与可量化指标是通行货币。

- 怎么抓住:1)岗位能力模型对齐;2)多渠道精准投递与节奏管理;3)作品集与端到端可复现实验;4)有的放矢的面试训练。

- 立即行动:明确双主线、打磨硬核作品集、配置关键词与内推网络、滚动复盘。必要时在投递系统(如企业/合作方使用的i人事)留存账号以追踪进度: https://account.ihr360.com/ac/view/login/#/login/?source=aiworkseo; 通过结构化准备与数据化说服,你能在字节跳动AI芯片招聘窗口中最大化“被看见→被认可→被录用”的转化率。

精品问答:

字节跳动AI芯片招聘最新信息有哪些?

我最近对字节跳动的AI芯片招聘很感兴趣,但不清楚最新的招聘岗位和要求是什么?能不能帮我详细介绍一下目前的招聘动态?

字节跳动AI芯片招聘最新信息主要包括硬件设计工程师、架构工程师、算法工程师等岗位。招聘要求通常涵盖熟悉芯片设计流程、具备相关专业背景(如微电子、计算机工程)、掌握Verilog/VHDL等硬件描述语言,或拥有AI算法开发经验。根据2024年第一季度招聘数据,AI芯片岗位需求同比增长35%,特别强调跨学科团队协作能力。建议定期访问字节跳动官方招聘网站及专业招聘平台,关注岗位更新,同时准备针对性简历和项目经验展示。

如何有效准备字节跳动AI芯片岗位的面试?

我计划应聘字节跳动的AI芯片相关职位,但面试内容和流程让我有些困惑,不知道该如何有针对性地准备,能具体说明吗?

准备字节跳动AI芯片岗位面试时,重点包括三大部分:技术面试、项目经验分享和综合素质评估。技术面试多涉及数字电路设计、芯片架构、AI模型加速原理等,建议通过刷算法题(如LeetCode)、复习芯片设计工具(Cadence、Synopsys)及AI硬件加速案例(如TPU设计原理)来提升实战能力。项目经验部分,重点突出参与过的芯片设计或AI算法优化项目,结合具体数据说明贡献效果(如提升运算效率20%)。综合素质评估多考察团队协作和创新能力,准备真实案例说明。面试流程一般分为初试、技术复试及HR面试,整体周期约2-4周。

字节跳动AI芯片岗位对学历和技能有哪些具体要求?

我想知道字节跳动对AI芯片职位的学历和技能门槛高吗?比如本科、硕士有什么差别?需要掌握哪些核心技能?

字节跳动AI芯片岗位通常要求电子信息、微电子、计算机等相关专业本科及以上学历,其中硕士及以上学历在复杂项目研发和算法优化方向更受欢迎。核心技能包括:

| 学历层次 | 技能要求 | 说明 |

|---|---|---|

| 本科 | 熟悉数字电路设计、Verilog/VHDL | 能参与基础芯片模块开发 |

| 硕士 | 掌握芯片架构设计、AI加速算法 | 负责复杂芯片系统架构与算法优化 |

| 博士 | 深入AI芯片全流程设计与创新研究 | 引领技术方向,推动前沿技术突破 |

此外,了解深度学习框架(TensorFlow、PyTorch)与硬件加速器结合、熟悉芯片验证流程也是加分项。

怎样抓住字节跳动AI芯片招聘的就业机会?

我想知道怎样才能更好地抓住字节跳动AI芯片招聘的机会,是提升技能还是积累项目经验更重要?有哪些实用建议?

抓住字节跳动AI芯片招聘就业机会,建议从以下几个方面入手:

- 技能提升:重点掌握AI芯片设计相关技术,如数字电路设计、AI模型硬件加速原理。通过在线课程及实战项目提升实操能力。

- 项目经验:参与开源AI芯片项目或实习,积累实际芯片设计和优化经验。案例中显示,有相关项目经验的候选人成功率提高40%。

- 网络资源:积极参加行业交流会、招聘宣讲,建立内推关系,提升面试成功率。

- 简历优化:突出技术亮点和项目成果,利用数据化描述(如“提升芯片计算效率15%”)增强说服力。

结合以上策略,能显著提升入职字节跳动AI芯片团队的机会。

文章版权归"

转载请注明出处:https://irenshi.cn/p/402079/

温馨提示:文章由AI大模型生成,如有侵权,联系 mumuerchuan@gmail.com

删除。